# How Fast Can Higher-Order Masking Be in Software?

Dahmun Goudarzi and Matthieu Rivain

EUROCRYPT 2017, Paris

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

$$\mathbf{x} = x_1 + x_2 + \dots + x_d$$

$$\mathbf{x} = x_1 + x_2 + \cdots + x_d$$

• Linear operations: O(d)

$$\mathbf{x} = x_1 + x_2 + \cdots + x_d$$

- Linear operations: O(d)

- Non-linear operations:  $O(d^2)$

$$\mathbf{x} = x_1 + x_2 + \dots + x_d$$

- Linear operations: O(d)

- Non-linear operations:  $O(d^2)$

- → Challenge for blockciphers: S-boxes

## Ishai-Sahai-Wagner Multiplication

$$\sum_{i} c_{i} = \left(\sum_{i} a_{i}\right) \times \left(\sum_{i} b_{i}\right) = \sum_{i,j} a_{i} \times b_{j}$$

$$\begin{pmatrix} a_1b_1 & a_1b_2 & \dots & a_1b_d \\ 0 & a_2b_2 & \dots & \vdots \\ \vdots & \vdots & & \vdots \\ 0 & 0 & \dots & a_db_d \end{pmatrix} + \begin{pmatrix} 0 & 0 & \dots & 0 \\ a_2b_1 & 0 & \dots & \vdots \\ \vdots & \vdots & & \vdots \\ a_db_1 & a_db_2 & \dots & 0 \end{pmatrix} + \begin{pmatrix} 0 & r_{1,2} & \dots & r_{1,d} \\ r_{1,2} & 0 & \dots & \vdots \\ & & \ddots & r_{d,d-1} \\ r_{1,d} & & r_{d,d-1} & 0 \end{pmatrix}$$

## The Polynomial Methods

• Sbox seen as a polynomial over  $GF(2^n)$

$$S(x) = \sum_{i=0}^{n} a_i x^i$$

## The Polynomial Methods

• Sbox seen as a polynomial over  $GF(2^n)$

$$S(x) = \sum_{i=0}^{n} a_i x^i$$

#### Generic Methods

$$S(x) = \sum_{i} (p_i \star q_i)(x)$$

- CRV decomposition,  $\star = \times$  (CHES 2014)

- Algebraic decomposition, \* = (CRYPTO 2015)

## The Polynomial Methods

• Sbox seen as a polynomial over  $GF(2^n)$

$$S(x) = \sum_{i=0}^{n} a_i x^i$$

#### Generic Methods

$$S(x) = \sum_{i} (p_i \star q_i)(x)$$

- CRV decomposition,  $\star = \times$  (CHES 2014)

- Algebraic decomposition, ★ = (CRYPTO 2015)

#### **AES Specific Methods**

$$S_{\text{AES}}(x) = \mathsf{Aff}(x^{254})$$

- RP multiplication chain (CHES 2010)

- KHL multiplication chain (CHES 2011)

#### Our results

- Optimized implementations of state of the art higher-order masking techniques

- Bottom-up approach:

- base field multiplication

- ► ISW/CPRR

- polynomial methods

- Finely tuned ARM assembly (parallelization)

- Alternative strategy: bitslice method (new AES and PRESENT speed records)

#### **ARM**

- 32-bit architecture with 16 registers (13 user accessible register)

- Barrelshifter: shifts and rotates virtually free

- **Example:** x-times and add on GF(2)[x] in 1 cycle

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

- Goal: efficient implementation of multiplication over  $GF(2^n)$

- Fastest method: precomputed look-up table

- Limitation: constrained memory on embedded system

| n          | 4        | 5     | 6     | 7      | 8      | 9       | 10       |

|------------|----------|-------|-------|--------|--------|---------|----------|

| Table size | 0.25 kiB | 1 kiB | 4 kiB | 16 kiB | 64 kiB | 512 kiB | 2048 kiB |

|              | bin mult v1 | bin mult v2    | exp-log v1     | exp-log v2         | kara.              | half-tab                  | full-tab      |

|--------------|-------------|----------------|----------------|--------------------|--------------------|---------------------------|---------------|

| clock cycles | 10n + 3     | 7n + 3         | 18             | 16                 | 19                 | 10                        | 4             |

| registers    | 5           | 5              | 5              | 5                  | 6                  | 5                         | 5             |

| code size    | 52          | $2^{n-1} + 48$ | $2^{n+1} + 48$ | $3 \cdot 2^n + 40$ | $3 \cdot 2^n + 42$ | $2^{\frac{3n}{2}+1} + 24$ | $2^{2n} + 12$ |

|              | bin mult v1 | bin mult v2    | exp-log v1     | exp-log v2         | kara.              | half-tab                  | full-tab      |

|--------------|-------------|----------------|----------------|--------------------|--------------------|---------------------------|---------------|

| clock cycles | 10n + 3     | 7n + 3         | 18             | 16                 | 19                 | 10                        | 4             |

| registers    | 5           | 5              | 5              | 5                  | 6                  | 5                         | 5             |

| code size    | 52          | $2^{n-1} + 48$ | $2^{n+1} + 48$ | $3 \cdot 2^n + 40$ | $3 \cdot 2^n + 42$ | $2^{\frac{3n}{2}+1} + 24$ | $2^{2n} + 12$ |

$$a \times b = \left( \mathbf{a}_h \, x^{\frac{n}{2}} + \mathbf{a}_\ell \right) \times \left( b_h \, x^{\frac{n}{2}} + b_\ell \right)$$

$$\mathsf{Karatsuba} = \mathrm{T1}[\ a_{\pmb{h}} \mid b_{h}\ ] + \mathrm{T2}[\ a_{\pmb{\ell}} \mid b_{\ell}\ ] + \mathrm{T3}[\ a_{\pmb{h}} + a_{\pmb{\ell}} \mid b_{h} + b_{\ell}\ ]$$

|              | bin mult v1 | bin mult v2    | exp-log v1     | exp-log v2         | kara.              | half-tab                  | full-tab      |

|--------------|-------------|----------------|----------------|--------------------|--------------------|---------------------------|---------------|

| clock cycles | 10n + 3     | 7n + 3         | 18             | 16                 | 19                 | 10                        | 4             |

| registers    | 5           | 5              | 5              | 5                  | 6                  | 5                         | 5             |

| code size    | 52          | $2^{n-1} + 48$ | $2^{n+1} + 48$ | $3 \cdot 2^n + 40$ | $3 \cdot 2^n + 42$ | $2^{\frac{3n}{2}+1} + 24$ | $2^{2n} + 12$ |

$$a \times b = (\mathbf{a}_h x^{\frac{n}{2}} + \mathbf{a}_\ell) \times (b_h x^{\frac{n}{2}} + b_\ell)$$

$$\mathsf{Half \ table} = \mathrm{T1}[\ a_h \mid a_\ell \mid b_h\ ] + \mathrm{T2}[\ a_h \mid a_\ell \mid b_\ell\ ]$$

|              | bin mult v1 | bin mult v2 | exp-log v1 | exp-log v2 | kara. | half-tab | full-tab |

|--------------|-------------|-------------|------------|------------|-------|----------|----------|

| clock cycles | 10n + 3     | 7n + 3      | 18         | 16         | 19    | 10       | 4        |

| registers    | 5           | 5           | 5          | 5          | 6     | 5        | 5        |

| code size    | 52          | 56 B        | 80 B       | 88 B       | 90 B  | 152 B    | 268 B    |

For n=4: full table

▶ Fastest multiplication: 4 clock cycles

▶ Low code size: 268 B

|              | bin mult v1 | bin mult v2 | exp-log v1 | exp-log v2 | kara. | half-tab | full-tab |

|--------------|-------------|-------------|------------|------------|-------|----------|----------|

| clock cycles | 10n + 3     | 7n + 3      | 18         | 16         | 19    | 10       | 4        |

| registers    | 5           | 5           | 5          | 5          | 6     | 5        | 5        |

| code size    | 52          | 176 B       | 560 B      | 808 B      | 810 B | 8216 B   | 64 kiB   |

- For n = 8: exp-log or half-tab

- ▶ tradeoff between clock cycles and code size

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

## Quadratic Operations

#### ISW

- ► Secure GF-mult of 2 operands

- ▶ Might need refreshing (see paper for details)

#### CPRR

- ▶ Evaluation of quadratic functions in 1 operand

- Similar to ISW: GF-mult → lookup tables

- ▶ Twice more random

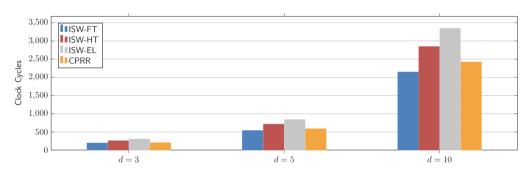

#### Performances Comparisons

- ISW < CPRR when table too huge

- Asymptotical comp: 1 CPRR → 1.16 ISW-FT, 0.88 ISW-HT, 0.75 ISW-EL

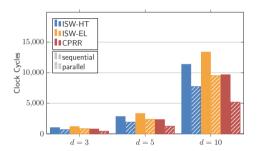

#### **Parallelization**

- 32-bit register filled with only *n*-bit elements

- Perform several ISW/CPRR in parallel:

- ▶  $n = 4 \rightarrow 8$  elements/register

- ▶  $n = 8 \rightarrow 4$  elements/register

- Consequence:

- ▶ Parallel: load, store, xor, loops

- ▶ Sequential: GF mult, CPRR lookups

#### Performances Gain of Parallelization

$$n = 8$$

(4 elements)

Asympt. ratio: CPRR 54%.

$$n = 4$$

(8 elements)

■ Asympt. ratio: ISW 42%.

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

$$S(x) = \sum_{i} q_i(x) \star p_i(x)$$

$$S(x) = \sum_{i} q_i(x) \star p_i(x)$$

lacksquare  $q_i$ : random linear combinations from a basis  $\mathcal{B}$

$$S(x) = \sum_{i} q_i(x) \star p_i(x)$$

- $\blacksquare q_i$ : random linear combinations from a basis  $\mathcal{B}$

- find  $p_i$  by solving a linear system

$$S(x) = \sum_{i} q_i(x) \star p_i(x)$$

- ullet  $q_i$ : random linear combinations from a basis  ${\cal B}$

- find  $p_i$  by solving a linear system

- CRV vs AD:

- ► CRV [CRV14]: \* = GF-multiplication → ISW multiplication

- ▶ AD [CPRR15]:  $\star =$  composition  $\rightarrow$  CPRR evaluation

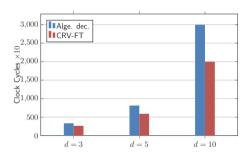

#### **CRV** Improvement

- Use CPRR for the basis computation

- **Example** for n = 8:

#### **CRV**

$$x^{3} = x \cdot x^{2}$$

$$x^{7} = x \cdot (x^{3})^{2}$$

$$x^{29} = x \cdot (x^{7})^{4}$$

$$x^{87} = x^{3} \cdot x^{29}$$

$$x^{251} = (x^{6})^{16} \cdot (x^{87})^{128}$$

5 ISW

#### This paper

$$x^{3} = x^{3}$$

$$x^{9} = (x^{3})^{3}$$

$$x^{5} = x^{5}$$

$$x^{25} = (x^{5})^{5}$$

$$x^{125} = (x^{25})^{5}$$

$$x^{115} = (x^{125})^{5}$$

6 CPRR

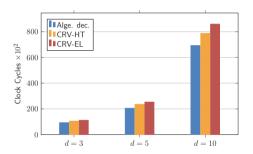

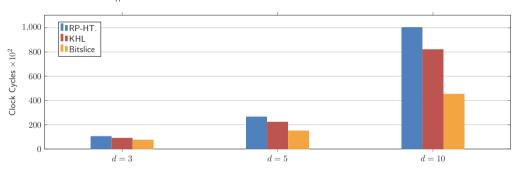

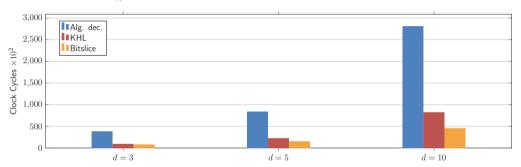

# Implementation Results

$n = 4 \ (8 \text{ s-boxes in } //)$

n = 8 (4 s-boxes in //)

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

## Polynomial Methods for AES

Based on the specific algebraic structure of the AES:

$$S(x) = \text{Aff}(x^{254})$$

21/32

- RP10 method : 4 ISW mult

- → Security flaw due to refreshing

- → Patch [CPRR13]: 1 CPRR + 3 ISW

- → Improvement [GPS14]: 3 CPRR + 1 ISW

- KHL11 method: 5 ISW mult on GF(16)

- → Patch [this paper]: 1 CPRR + 4 ISW

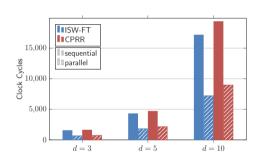

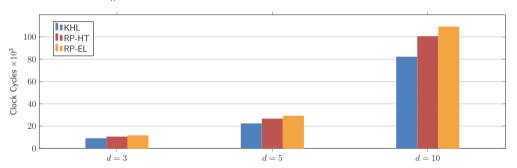

#### Implementation Results

■ 16 s-boxes in //

■ KHL < RP-\*: smaller elements → higher parallelization degree

- 1 Introduction

- 2 Field Multiplications

- 3 Non-Linear Operations

- 4 Generic Polynomial Methods

- 5 Polynomial Methods for AES

- **6** The Bitslice Strategy

#### Bitslice for the AES

Sbox seen as boolean circuit

■ 16 S-boxes in //

## Application for AES S-boxes

- Circuit for the AES S-box [BMP13]

- ▶ 83 XOR gates

- ▶ 32 AND gates

- Bitslice (16 s-boxes)

- ▶ 83 XOR instructions

- ▶ 32 AND instructions

- Masking at the order *d*:

- $\blacktriangleright$  83  $\times$  d XOR instructions

- ▶ 32 ISW-AND

## Improvement

#### 2 16-bit ISW-AND → 1 32-bit ISW-AND

- Goal: grouping AND gates per pairs

- Validation on BMP circuit

- 16 s-boxes = 16 ISW-AND → 1 ISW-AND per s-box

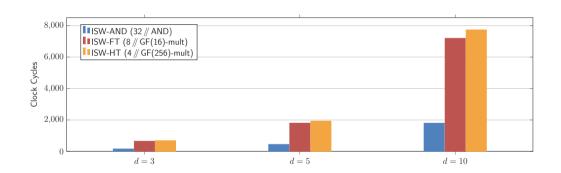

## Performance Comparison of ISW

### Performances for AES S-box

■ 16 S-boxes in //

- RP-HT: 1 ISW-HT/CPRR per s-box

- KHL: 0.83 ISW-FT/CPRR per s-box

- Bitslice: 1 ISW-AND per s-box

### **AES** vs Generic

■ 16 S-boxes in //

CPYPTO EXPERTS ...

- KHL  $3.1 \times$  faster than AD (for n = 8)

- Bitslice 2.3× faster than KHL

## Timing for AES and PRESENT Block-Cipher

|                  | d=2                | d=3                | d=4                   | d=5                | d = 10             |

|------------------|--------------------|--------------------|-----------------------|--------------------|--------------------|

| Bitslice AES     | $0.89~\mathrm{ms}$ | $1.39~\mathrm{ms}$ | $1.99~\mathrm{ms}$    | $2.7~\mathrm{ms}$  | 8.01 ms            |

| Bitslice PRESENT | $0.62~\mathrm{ms}$ | $0.96~\mathrm{ms}$ | $1.35 \; \mathrm{ms}$ | $1.82~\mathrm{ms}$ | $5.13~\mathrm{ms}$ |

Clock frequency: 60 MHZ

Case study on ARM: barrelshifter and 32-bit registers

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- ▶ For n = 4, full tabulated (4 clock cycles and 268B)

- ullet For n-8, trade-off between exp-log and half-table

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- For n=4, full tabulated (4 clock cycles and 268B)

- $\blacktriangleright$  For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ▶ CPRR > ISW when table too huge

- ► Smaller elements → higher parallelization degree

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- For n=4, full tabulated (4 clock cycles and 268B)

- $\blacktriangleright$  For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ▶ CPRR > ISW when table too huge

- ► Smaller elements → higher parallelization degree

- Generic polynomial methods:

- ▶ New optimal parameters for CRV with CPRR evaluations

- ightharpoonup Depending on n, trade-off between AD and CRV

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- ▶ For n = 4, full tabulated (4 clock cycles and 268B)

- ▶ For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ▶ CPRR > ISW when table too huge

- ► Smaller elements → higher parallelization degree

- Generic polynomial methods:

- ▶ New optimal parameters for CRV with CPRR evaluations

- ightharpoonup Depending on n, trade-off between AD and CRV

- Polynomial methods for AES:

- ▶ KHL > RP because of manipulations of higher parallelization degree

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- For n=4, full tabulated (4 clock cycles and 268B)

- $\blacktriangleright$  For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ▶ CPRR > ISW when table too huge

- ► Smaller elements → higher parallelization degree

- Generic polynomial methods:

- ▶ New optimal parameters for CRV with CPRR evaluations

- ightharpoonup Depending on n, trade-off between AD and CRV

- Polynomial methods for AES:

- ▶ KHL > RP because of manipulations of higher parallelization degree

- Pushing the parallelization to the optimal: bitslice strategy

- ▶ Reordering of Boolean circuit for optimal use of registers

- ▶ Better than any polynomials methods for AES and Present

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- For n=4, full tabulated (4 clock cycles and 268B)

- ▶ For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ▶ CPRR > ISW when table too huge

- ▶ Smaller elements → higher parallelization degree

- Generic polynomial methods:

- ▶ New optimal parameters for CRV with CPRR evaluations

- ▶ Depending on n, trade-off between AD and CRV

- Polynomial methods for AES:

- ▶ KHL > RP because of manipulations of higher parallelization degree

- Pushing the parallelization to the optimal: bitslice strategy

- ▶ Reordering of Boolean circuit for optimal use of registers

- ▶ Better than any polynomials methods for AES and Present

- → Can we use Bitslice for generic methods?

- Case study on ARM: barrelshifter and 32-bit registers

- Selection of best field multiplication algorithms:

- ▶ New proposed method: half-table

- ▶ For n = 4, full tabulated (4 clock cycles and 268B)

- $\blacktriangleright$  For n-8, trade-off between exp-log and half-table

- Optimization of non-linear operations

- ightharpoonup CPRR > ISW when table too huge

- ► Smaller elements → higher parallelization degree

- Generic polynomial methods:

- ▶ New optimal parameters for CRV with CPRR evaluations

- ightharpoonup Depending on n, trade-off between AD and CRV

- Polynomial methods for AES:

- ▶ KHL > RP because of manipulations of higher parallelization degree

- Pushing the parallelization to the optimal: bitslice strategy

- ▶ Reordering of Boolean circuit for optimal use of registers

- ▶ Better than any polynomials methods for AES and Present

- $\rightarrow$  Can we use Bitslice for generic methods? Yes, GR16 [CHES 2016]

# Questions?